## DCEL101

|          |   | <br>_ |  | , |

|----------|---|-------|--|---|

| Reg. No. | 2 |       |  |   |

### I Semester B.Sc. Degree Examination, April - 2023 ELECTRONICS

# Electronics Devices and Circuits

Paper: ELE - CT - 1

(NEP Scheme 2020)

Time: 21/2 Hours

Maximum Marks: 60

Instructions to Candidates:

Answer all the questions from Part -A, any Four questions from Part -B and any FOUR questions from Part -C.

Note: (Answer all questions of Part – A in any one page, the same questions answered multiple times will not be considered for Evaluation.)

|                              |      |       |             |              | 0.0      | PART    | `-A   |                             | ,                    |

|------------------------------|------|-------|-------------|--------------|----------|---------|-------|-----------------------------|----------------------|

| Answer all the subdivisions. |      |       |             |              |          |         |       |                             | $(12 \times 1 = 12)$ |

| 1.                           | i)   | Inte  | rnal resist | ance of an   | Ideal V  | oltage  | sour  | ce                          | •                    |

|                              |      | a)    | one         | · ·          |          |         | b) 1  | infinity                    |                      |

|                              |      | c)    | zero        |              |          |         | d)    | none of the above           |                      |

|                              | ii)  | The   | algebraic   | sum of vo    | ltage in | any cl  | osed  | path of network is equal to |                      |

|                              |      | a)    | zero        | · · ·        |          |         | b)    | infinity                    |                      |

|                              |      | c)    | one         |              | : e      |         | d)    | two                         | 7                    |

|                              | iii) | The   | oretical v  | alue of effi | ciency   | for a h | alf-w | rave rectifier is           |                      |

|                              |      | a)    | 33.3%       |              | •        |         | b)    | 40.6%                       | •                    |

|                              | ٠.   | c)    | 66.6%       | r            |          | ·•      | d)    | 72.9%                       |                      |

|                              | iv)  | The   | output vo   | ltage of IC  | 7915 v   | oltage  | regu  | lator is                    |                      |

|                              |      | a)    | +15V        |              |          |         | b)    | –5V                         |                      |

|                              |      | . (2) | +5V         |              |          |         | d)    | -15V                        |                      |

- v) Which of the following points locate the quiescent point in CE mode

- a)  $(I_C, V_{CE})$

b)  $(I_{E}, V_{CB})$

c)  $(I_{B}, V_{CE})$

- d)  $(I_c, V_{cc})$

- vi) β gain of the transistor indicates

- a) Regulation capability

- b) Amplification capability

- c) Rectification capability

- d) All of the above

- vii) Which of the following is the universal biasing circuit

- a) Collector to base bias

- b) Voltage divider bias

c) Emitter bias

- d) Fixed bias

- viii) Which amplifier is used for unity voltage gain

- a) CC Amplifier

b) CB Amplifier

c) CE Amplifier

- d) None of the above

- ix) What is the input voltage of an amplifier with gain of 100 to generate 10V output?

- . a) 1V

b) 100mV

c) 10mV

- d) lmV

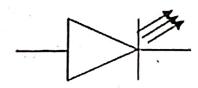

- x) Identify the component shown in the figure

a) Zener diode

b) Junction diode

c) Schottky diode

- d) Light emitting diode

- xi) The BCD Code for decimal number 22

- a) 0000 0010

b) 0010 0010

c) 0001 0110

- d) 0010 0000

- xii) \_\_\_\_\_ is a Universal logic gate

- a) NAND

b) XOR

c) OR

d) AND

### DCEL101

#### PART-B

## Answer any Four of the following questions.

$(4 \times 7 = 28)$

2. State Maximum power transfer theorem and explain with an example.

(7)

- 3. Draw the block diagram of regulated power supply and explain its functional blocks. (7)

- 4. a) Explain the operation of a NPN transistor.

- b) Establish the relation between  $\alpha$  and  $\beta$ .

(5+2)

- 5. With circuit diagram explain the working principle of single stage CE amplifier and draw the frequency response curve. (7)

- 6. With an example explain the method to convert decimal number to binary and Hexadecimal equivalent. (7)

- 7. a) State and verify De Morgan's theorem.

- b) Verify the universal property of NAND gate by realizing OR gate.

(5+2)

#### PART-C

### Answer any Four of the following questions.

$(4 \times 5 = 20)$

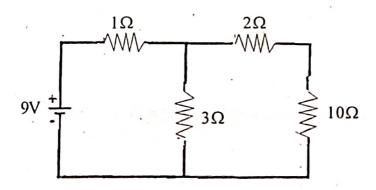

8. Find the value of current through  $10\Omega$  resistor in the given circuit using Thevenin's theorem.

9. Calculate the efficiency and  $V_{DC}$  of a HWR with an input voltage of 250V rms and load resistance of 20  $\Omega$ , with turns ratio 10:1.

- 10. Draw the DC load line and mark the operating point for the voltage divider biasing circuit using silicon transistor. Given  $\beta$ =200,  $R_1$ =1 1K $\Omega$ ,  $R_2$  = 3.2K $\Omega$ ,  $R_C$  = 1.3K $\Omega$ ,  $R_E$  = 750 $\Omega$  and  $V_{CC}$  = 9V.

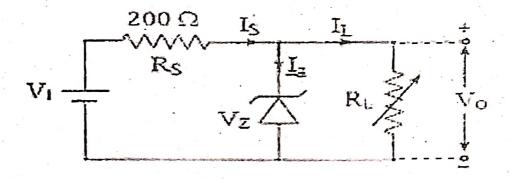

- 11. Calculate  $R_{L(min)}$  and  $R_{L(max)}$  in the circuit shown for getting regulated output voltage. Given:  $V_z = 5.6V$ ,  $V_I = 30 \text{ V}$  and  $I_{Z(max)} = 25 \text{ mA}$ .

- 12. a) Subtract 30H from 7DH using 2's complement method.

- b) Add (110110)<sub>2</sub> and (110110)<sub>2</sub> express the result in decimal. (3+2)

- 13. Simplify the expression  $Y = A \cdot \overline{B} \cdot C + \overline{A} \cdot B(B \cdot C + \overline{B})$  using Boolean laws and draw the circuit for simplified expression using basic gates.